Реверсивные тиристорные преобразователи с раздельным управлением

Для построения временной диаграммы и последующего использования разработаем в Simulink модель логического переключающего устройства LPU (рис. 1.127). Схема модели блока LPU раскрыта на рис. 1.125. ЛПУ имеет два входа: DST — датчик состояния тиристоров (при всех закрытых тиристорах на выходе датчика действует единичный логический сигнал) и напряжение задания Uz. Порядок переключения вентильных… Читать ещё >

Реверсивные тиристорные преобразователи с раздельным управлением (реферат, курсовая, диплом, контрольная)

Модель логического переключающего устройства

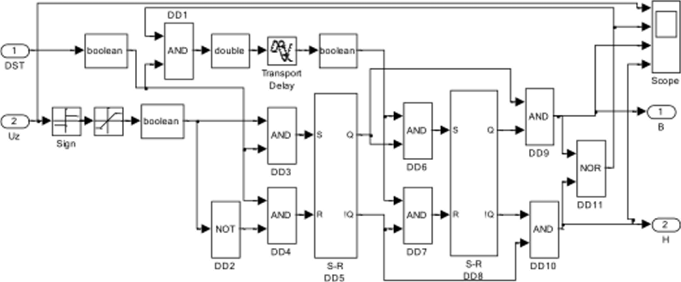

Порядок переключения вентильных групп (преобразователей) организует логическое переключающее устройство (ЛПУ), структура которого [4, 5] показана на рис. 1.125.

Рис. 1.125. Структурная схема логического переключающего устройства LPU

Рис. 1.126. Временная диаграмма работы ЛПУ

По своей структуре преобразователи с раздельным управлением просты: выходы двух преобразователей включены встречно параллельно. Полярность выходного напряжения определяется включенным комплектом. Первая особенность управления состоит в организации порядка переключения комплектов управляемых выпрямителей.

ЛПУ имеет два входа: DST — датчик состояния тиристоров (при всех закрытых тиристорах на выходе датчика действует единичный логический сигнал) и напряжение задания Uz.

Для пояснения принципа работы примем сигнал DST = /, а напряжение задания Uz меняется во времени от +10 до минус 10 В (см. временную диаграмму работы ЛПУ на рис. 1.126). Аналоговый сигнал задания Uz с помощью блоков Sign, Saturation и Boolean преобразуется в логический, причём положительному напряжению Uz соответствует логическая единица, отрицательному — ноль.

Для построения временной диаграммы и последующего использования разработаем в Simulink модель логического переключающего устройства LPU (рис. 1.127). Схема модели блока LPU раскрыта на рис. 1.125.

Рис. 1.127. Схема модели LPU (Fig 1 _127)

Рассмотрим временную диаграмму (рис. 1.126), полученную при исполнении файла Figl127.

В начальный момент времени (1 = 0) в триггер DD5 записывается единица, так как на входе DST действует единица и единица на входе S триггера DD5 (Uz>0). Триггер DD8 по умолчанию при нулевых сигналах на входах S и R включается в нулевое состояние (на прямом выходе Q = 0). На выходах DD9 и DD10 появляются нули (триггеры DD5 и DD8 находятся в рассогласованном состоянии) и на выходе DD11 появляется единица. Если тиристоры закрыты (единица на входе DST), то запускается с выхода DD1 линия задержки. Единица с выхода DD1 появится на входах записи DD6, DD7 через время, установленное в блоке Transport Delay. После истечения указанного времени триггер DD8 переводится в единичное состояние (согласованное с DD5) и разрешается включение первого комплекта управляемого выпрямителя (появляется сигнал высокого уровня на выходе В). Отметим, что в начальный момент времени действовал запрет на включение в работу обоих выпрямителей.

В момент смены полярности задающего напряжения Uz меняется логический уровень управления состоянием триггера DD5 и если все тиристоры выпрямительных групп закрыты, то DD5 меняет состояние на противоположное (нулевое). Опять триггеры DD5 и DD8 находятся в несогласованном состоянии, запрещается управление выпрямителями, на выходе ООП появляется единица, которая через время задержки (при условии закрытого состояния всех тиристоров) поставит в согласованное состояние триггеры, и разрешит включение комплекта Н. Все эти рассуждения, подкрепленные результатами моделирования, представлены на рис. 1.126.