ОБ предназначен для выполнения логических, арифметических и сдвиговых операций над поступающими на его вход данными. Также в его задачи входит формирование адреса следующей микрокоманды и формирование признаков результата операции.

ОБ также может влиять на формирование следующего адреса в МУУ посредством передачи в него признака ветвления.

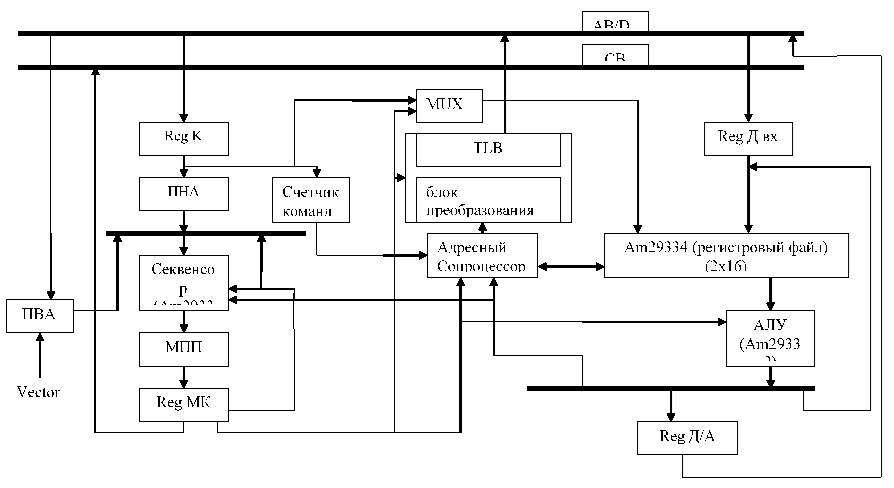

Операционный блок включает в себя:

- · арифметико-логическое устройство (Am29332, 32-разрядный)

- · регистровый файл (Am29334, 2×16-разрядный)

- · буферные регистры (регистр входных данных, регистр выходных данных и адресный регистр);

Структурная схема операционного блока изображена на рис. 4.

Рис. 4 Структурная схема операционного блока

С началом нового цикла в регистр входных данных помещаются данные с шины AB/DB и поступают на входную шину регистрового файла. Запись и чтение в регистровый файл производится по адресу, который берется, либо из соответствующего поля регистра команд, либо из Reg МК (выбирается с помощью MUX). Выходная шина регистрового файла управляется из МК, чтобы можно было ее использовать для передачи константы из Reg МК. Далее данные прочитанные из регистрового файла или константа из МК поступают на входы либо АЛУ, либо сопроцессора (рис. 7).

Вывод данных из процессорных элементов производиться на локальную шину, из которой данные поступают на вход регистрового файла и регистра данных. Адреса могут формироваться только в ПЭ, поэтому адресный КЭШ подключен напрямую к выходу ПЭ (рис. 7).

Флаги, генерируемые процессорными элементами, поступают на вход тестирования внешних условий секвенсера микрокоманд (рис. 7).

На процессорные элементы данные поступают из соответствующих трактов регистрового файла. Управление процессорными элементами производится микропрограммой. Из микрокоманды поступают соответствующие биты на входы управления ПЭ. Также микрокомандой, в зависимости от типа операции, производиться приостановка одного из процессорных элементов, запрещение/разрешение вывода данных регистрам адреса и данных, запрещение/разрешение записи данных по тракту в регистровый файл. Микропрограмма управляет работой адресного КЭШа, разрешает/запрещает запись в таблицу сегментов или страниц. Также разрешает/запрещает преобразование виртуальных адресов в физические. Данная опция необходима, в случае, когда происходит обращение к периферийному устройству по полученному вектору прерывания. Потому что, после сложения вектора значения прерываний с содержимым базового регистра, получается физический адрес устройства.